边沿触发器与计数器 计算机时序逻辑的基石

在探索计算机软硬件背后隐秘语言的过程中,我们抵达了一个构建现代数字系统心脏的关键节点:时序逻辑电路。第14章将焦点对准了两种基础而强大的元件——边沿触发器和由它们构成的计数器,它们共同为计算机的“节奏”与“记忆”奠定了基础。

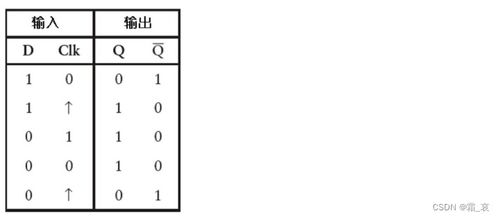

边沿触发器是数字电路中的一种基本存储单元,其核心特性在于仅在时钟信号的特定跳变时刻(上升沿或下降沿)捕获并锁存输入数据的状态,而非在整个时钟电平期间都响应。这种边沿触发的机制,对比于早期简单的电平触发锁存器,提供了更高的抗干扰能力和可靠性。当时钟边沿到来时,触发器采样此时的输入值(如D触发器的D端),并将该值保持到输出端,直至下一个有效时钟边沿。这一特性使得电路行为在时间上被精确离散化,确保了即使在有噪声或路径延迟存在的复杂系统中,数据也能在确定的时刻被稳定存储和传递,这是实现同步数字系统的前提。

将边沿触发器作为构建模块,我们可以创造出功能丰富的时序电路,其中计数器是最典型和广泛应用的代表之一。计数器本质上是一组相互连接的触发器,其状态按照预定的序列(通常是二进制序列)随每个时钟脉冲而规律变化。例如,一个由4个D触发器构成的4位二进制异步计数器,每个触发器的输出作为下一个触发器的时钟信号,从而实现从0000到1111的循环计数。更复杂、速度更快的同步计数器,则将所有触发器的时钟端连接在一起,通过组合逻辑来控制次态,实现精确的同步翻转。

在计算机的软硬件层面,计数器的作用无处不在且至关重要:

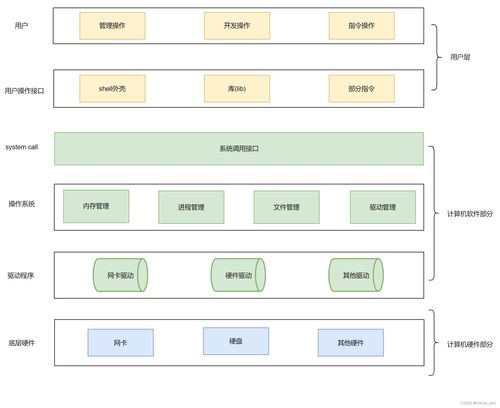

- 硬件层面:计数器是CPU中程序计数器(PC)的核心物理实现。程序计数器保存着下一条待执行指令的内存地址,每完成一条指令的取指,它就自动加1(或根据跳转指令被置入新值),从而驱动指令执行的顺序流。计数器还用于生成定时信号、分频、测量时间间隔、控制存储器地址序列等,是协调硬件各部件时序运作的节拍器。

- 软件与系统层面:软件程序员虽不直接操纵触发器,但程序的行为完全依赖于底层计数器创造的时序环境。操作系统的时间片轮转调度、定时器中断、性能计数器的读取,乃至高级编程语言中的循环控制变量,其本质都映射到底层硬件计数器的递增与比较操作。计数器定义了计算机对时间流逝和事件次序的量化感知。

因此,边沿触发器提供了数字记忆的“原子”,而计数器则将这些原子组织成能够“计数时间”与“序列状态”的有机体。它们共同隐匿在芯片的深处,将连续的物理时间转化为离散的逻辑步骤,使得计算机能够一步一步、有条不紊地执行软件指令,从最底层的硬件振荡到最上层的软件运行,构成了计算过程可靠进行的时序骨架。理解它们,就理解了计算机如何从一个瞬间到下一个瞬间,有序地创造奇迹。

如若转载,请注明出处:http://www.kanyingkeji.com/product/61.html

更新时间:2026-02-24 23:41:25